2020年EDA行业领军企业国微集团大动作频频,继自动化布局布线工具之后,又、重量级产品已经蓄势待发 -- 硬件仿真加速器即将震撼发布。

这款硬件仿真加速器,特点在于可显著提升芯片或系统级设计的验证效率,帮助芯片研发企业在保证产品质量和性能的基础上缩短研发周期,对整个行业的发展具有重要意义。它的研发成功,标志着国产化硬件仿真加速技术又将迈向一个新的里程碑。

随着芯片设计规模不断增加、工艺复杂度逐年提高,传统仿真工具在时间上、可容纳设计上以及验证完整性上都难以满足业内需求。EDA硬件仿真加速器在此时应运而生,将硬件加速技术和电路仿真技术融合在一个平台内,同时具备创新的软件自动化流程,可支持用户在更短的平台建立时间内,更高效地对芯片进行调试纠错,尤其对大型及超大型设计效果显著。

颠覆传统验证方式,“精度”与“速度”两者兼具

更短的平台建立时间:支持多种协议接口和丰富的IP资源,可以实现硬件到软件的快速建立和使用,无缝对接仿真。

极快的编译速度:支持多种硬件编程语言和验证模式,从RTL级别到网表级别全覆盖。

精准的功耗分析:帮助设计师验证并设计出更低功耗更高性能的产品。

超高的仿真吞吐量:可容纳10亿门设计,对大型设计可操作性强。

高效的调试纠错能力:支持动态、静态探针以及多种调试工具,从RTL级别到单个信号级别全可视。

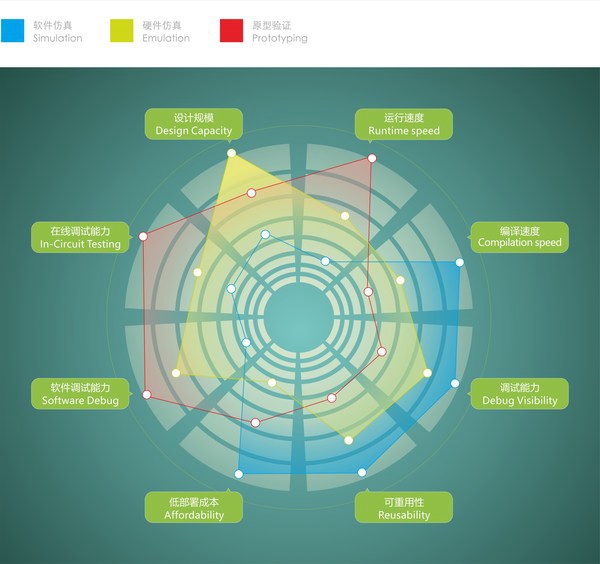

芯片验证是芯片设计中关乎最终成败的关键环节。完整的芯片验证可以保证流片后的产品质量,但过长的验证时间又可能导致产品错过最佳投放市场的时间。只有兼具“精度”和“速度”的芯片验证方式,才是芯片设计企业梦寐以求的方案。

国微集团研发的硬件仿真加速器就拥有高效的调试纠错能力,以及精准的功耗分析,保证了芯片验证的“精度”;大大缩短了平台建立时间、提高了编译速度和超高的仿真吞吐量,保证了芯片验证的“速度”。

这款硬件仿真加速器是基于全球先进的FPGA商用芯片,并符合中国芯片市场需求的调试和验证工具。它具备基于事务加速和基于断言加速的系统管理,支持丰富的编程语言。不仅在编译和运行速度上优于同类产品,还拥有强大的调试功能和良好的可操作性。它的推出会让我国自主研发集成电路产业向前迈进了一大步。

某芯片设计厂家曾多次表态:“企业级的芯片验证方案是现在我们迫切需要的,尤其是我国自主知识产权的产品。不但现在中国企业需要,我相信在未来的几年也会被更多国家和企业所采用。”

硬件仿真加速器是企业级芯片验证不可或缺的工具。它能让系统级的事务得以和硬件中运行的加速设计互动,将验证工程师从错综复杂的信号和管脚中解放出来,在应用和事件层面进行自动化的测试验证。硬件仿真加速器的使用者还可以选择自动运行全系统确认和软硬件协同验证,其能记录过程现象后启用离线分析,从而更高效地利用设备。

集“实用性”与“性价比”于一身,好用不贵

国微集团自主研发的硬件仿真加速器,是迄今为止功能最多的验证引擎,被用于任何规模和任何类型的设计。

它们可以验证硬件、集成硬件和嵌入式软件,也可以验证嵌入式软件和整个片上系统(SoC) 设计,还可以作为硅前开发的完整系统环境使用。无论从节约的验证周期计算,还是从复杂的调试情景所需的能力,包括工具的多用性都能看出,硬件仿真加速器已成为所需资金投入较少的验证解决方案。

效率究竟有多高?不断提升的编译速度和优化的编译算法,缩短了被测设计到硬件仿真加速器的映射时间。这部分工作曾经非常耗时,但现在已从数个月缩短为几天时间。如果设计复杂度较低时,甚至只需,。

国微集团将多年芯片开发经验融入到EDA工具的研发中,所发布的硬件仿真加速器,凭借企业级的可靠性和可扩展性,能帮助芯片研发企业更快、更省、更全面得完成芯片验证和设计使用,满足了市场对硬件仿真加速技术不断发展的需求。

耕耘二十七载,积微成著,铸芯筑魂

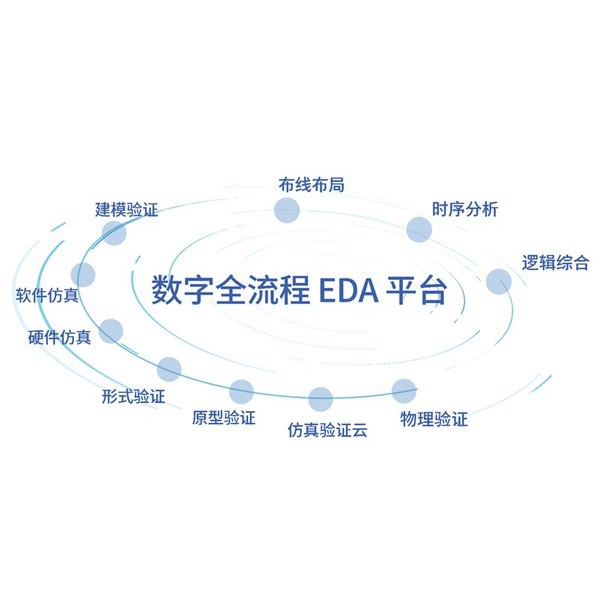

国微集团最初建立于1993年,是国家规划布局内的,软件企业及国家高新技术企业。2018年,国微集团承接了国家“十三五”重大科技专项“芯片设计全流程EDA系统开发与应用”,致力于通过自主研发、吸收引进、产学研结合、投资并购并举的策略,在EDA领域全面布局,打造本土自主可控数字全流程EDA。

在EDA工具方面,国微集团具有自动化布局布线工具,硬件仿真系统和原型验证系统三个,产品。

当前,EDA硬件仿真加速器上市在即,企业级的芯片验证加速时代即将到来,跨越式的机遇与挑战,也将验证国微集团本土化的决心和实力。